日本電気株式会社

セキュアシステムプラットフォーム研究所

委員名:山本剛

研究概要

量子アニーリングは、組合せ最適化問題を解くための計算手法の一つです。我々は、独自の量子アニーリングマシンを実現するために、スケールアウトが容易な超伝導量子素子、極低温実装技術、 これらのハードウェアを制御するための量子アニーリング理論の研究開発を進めています。これらの研究開発により、従来技術をはるかに上回るスピードで組合せ最適化問題を計算できる量子アニーリングマシンの実用化を目指します。さらには、量子アニーリング技術のユースケース拡充を図り、 時間短縮やエネルギーの削減などの、社会的な変革の推進により、明るく豊かな社会づくりに貢献していきます。

1超伝導回路を用いた量子ビット開発

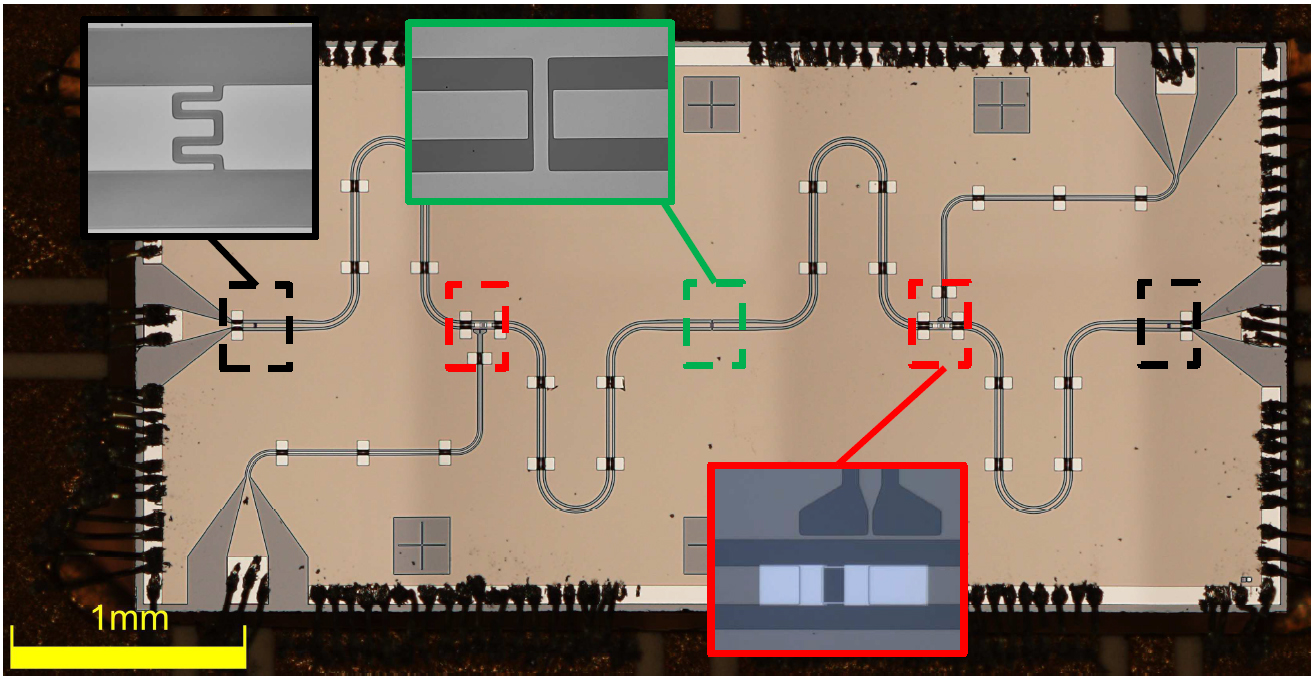

超伝導回路を用いて量子ビット(量子コンピュータで情報を扱う最小単位)を実現する研究を行っています。具体的には、超伝導パラメトロンと呼ばれる、非線形なインダクタンスを持つ超伝導のLC共振回路の2つの発振状態を0,1状態として利用するタイプの量子ビットを研究しています。現在は少数ビットの動作確認の段階ですが、将来の量子ビットの大規模集積化を目指して、素子の設計からクリーンルーム内でのデバイス作製プロセス、希釈冷凍機を用いた評価とデータ解析までを、産総研新原理コンピューティング研究センターと緊密に連携しながら行っています。

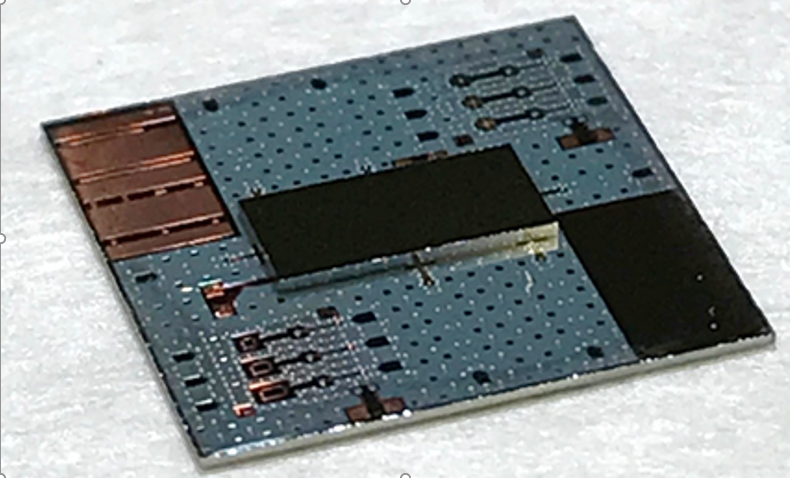

また、量子コンピュータを構成する量子ビットを多数・高密度で構成し、適切に外部との処理信号のやり取りを行うことを目的として、例えば、量子チップをインターポーザ(中間基板)にフリップチップ接続する3次元実装構造を研究開発しています。特にインターポーザにおいて、量子ビットの性能を低下しない材料構成や電磁界環境を考慮した回路設計、極低温動作における応力やひずみへの耐性を有する接続構造や全体構造などの研究を行っています。